# Single-Grain Si TFTs Fabricated by the **m**Czochralski (Grain-Filter) Process on a Large Glass Substrate

Yasushi Hiroshima, Chiharu Iriguchi, Ryoichi Ishihara\*, Satoshi Inoue, Tatsuya Shimoda, J.W.Metselaar\* and C.I.M Beenakker\* Technology Platform Research Center, SEIKO EPSON Corporation 281 Fujimi, Suwa-gun, Nagano-ken 399-0293, JAPAN Tel: +81 266 62 8445, FAX: +81 266 62 8998, E-mail: hiroshima.yasushi@exc.epson.co.jp \*Delft Institute of Microelectronics and Submicrontechnology (DIMES), Delft Univ. of Technol., Delft, The Netherlands

Location-controlled Si grains are prepared on a large glass substrate for the first time by the  $\mu$ -Czochralski (grain-filter) process. The maximum diameter of the Si grains is around 7  $\mu$ m, and EBSD and TEM analysis show that the Si grains contain few defects except coincidence site lattice (CSL) boundaries. Owing to the crystalline quality of the Si grains, single-grain Si TFTs obtained from the process give a high field-effect mobility of 512 cm<sup>2</sup>/Vs and a low subthreshold swing of 0.16 V/dec.

# 1. Introduction

Single-grain Si (sg-Si) TFTs fabricated on glass have been a key technology for not only future System on Glass, but also System on Plastic, which can be realized with SUFTLA technology<sup>1)</sup>. For producing the sg-Si TFTs, it is essential to control the position of Si grains and enlarge the Si grains. The  $\mu$ -Czochralski (grain-filter) process allows us to control the positions of Si grains precisely and to enhance the grain growth with a long pulsed laser<sup>2)</sup>. However, it was very hard to develop the process on a large glass substrate, because the grain-filter, a small hole with a diameter of about 100 nm, has to be formed.

Technologies for fine patterning of large glass substrates have recently been developed; sub-micron poly-Si TFTs already existed<sup>3)</sup>. Using these technologies, we have successfully developed the µ-Czochralski process on a large glass substrate.

This paper describes the evaluation of Si grains prepared on a large glass substrate by the  $\mu$ -Czochralski process with the fine patterning technologies. It also describes our investigation into characteristics of sg-Si TFTs and sub-micron sg-Si TFTs obtained from the process.

## 2. Experiments

The samples used in this study were fabricated through the  $\mu$ -Czochralski process. Firstly, small holes with a diameter and a depth of 0.6  $\mu$ m and 650 nm, respectively, are formed in a SiO<sub>2</sub> film on a 300  $\times$  300 mm<sup>2</sup> glass substrate by using Holographic Mask Aligner (HMA) systems and Inductive Coupled Plasma (ICP) etching systems, by which sub-micron patterning on the substrate

can be realized<sup>3)</sup>. Secondly, a 550-nm-thick TEOS PECVD SiO<sub>2</sub> film was deposited over the structure to reduce the hole diameter to around 100 nm. The resultant smaller holes are called a grain-filter. Thirdly, a-Si film with a thickness of 150 nm was deposited using LPCVD at 425°C on the SiO<sub>2</sub> film with the grain-filter. Lastly, the a-Si film was crystallized by a XeCl excimer laser with a duration time of about 200 ns at various energy densities. Some of the samples were heated at 400°C during the laser crystallization.

In the TFT fabrication process, oxygen plasma treatment was carried out after the laser crystallization. A gate insulator with a thickness of 40 nm was prepared by TEOS-PECVD, and annealed at 330°C for an hour in a steam ambient.

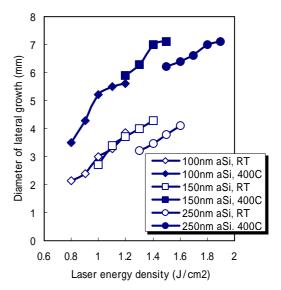

Fig. 1. Diameters of Si lateral growth as a function of laser energy density for various a-Si thickness and substrate temperatures.

#### 3. Results and discussions

Figure 1 shows the diameters of Si grain growth after laser irradiation. The diameters increase with laser energy density and substrate temperature, and a maximum diameter of around 7  $\mu$ m is obtained. This maximum diameter is larger than that prepared on a Si wafer as reported in AM-LCD'03<sup>2</sup>). An electron backscatter diffraction (EBSD) analysis showed that the Si grains included coincidence site lattice (CSL) boundaries like  $\Sigma$ 3,  $\Sigma$ 9 and  $\Sigma$ 27 without random grain boundaries.

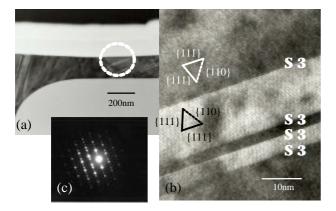

Figure 2(a) and 2(b) show cross-sectional TEM images of CSL boundaries located around the grain-filter. Crystal lattices with few defects and some planar faults can be observed in Fig. 2(b).

Fig. 2. Cross-sectional TEM images of CSL boundaries and an electron diffraction pattern of the observation area.

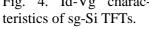

Fig. 5. Subthreshold swings of sg-TFTs with various channel lengths.

According to identifications of the crystallographic orientations, the planar faults are parallel to {111} planes, and the misorientation between both sides is 70.5° rotation along the <110> axis, which corresponds to  $\Sigma 3$ . These crystallographic orientations are also confirmed by an electron diffraction pattern as shown in Fig. 2(c).

In Raman spectroscopy analysis, a tensile stress of around  $1 \times 10^{10}$  dyn/cm<sup>2</sup>, which is similar to that of conventional laser crystallized poly-Si film, was observed inside the Si grains.

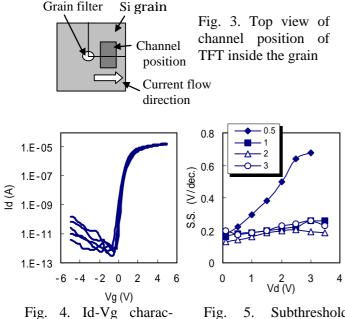

Sg-TFTs with a Si film thickness of 150 nm were fabricated at a shifted position from the grain-filter as shown in Fig. 3 to avoid CSL boundaries around the grain-filter<sup>2)</sup>. Figure 4 shows the transfer characteristics of the sg-Si TFTs with a channel length and a channel width of 1 µm and 1.7 µm, respectively. A field-effect mobility of 512 cm<sup>2</sup>/Vs and a subthreshold swing of 0.16 V/dec. are obtained on average at a drain voltage (Vd) of 0.1 V. Figure 5 shows subthreshold swings of sg-TFTs with channel lengths of 0.5, 1, 2 and 3  $\mu$ m as a function of Vd. The subthreshold swing of the sg-TFTs with a channel length of 0.5 µm increases with Vd. This is caused by a short channel effect with drain-induced barrier lowering (DIBL). This is also observed in output characteristics of the sub-micron sg-TFT as increments of source-drain leakage current. To avoid the DIBL, channel Si film thickness should be decreased.

### 4. Conclusions

Location-controlled large Si grains with few defects are prepared on a large glass substrate by the  $\mu$ -Czochralski process. The sg-Si TFTs yielded by the process exhibited a high mobility of 512 cm<sup>2</sup>/Vs and a low subthreshold swing of 0.16 V/dec. The sub-micron sg-Si TFT shows the short channel effect, which is due to relatively thick channel Si film.

#### References

[1] S. Inoue, S. Utsunomiya, T. Saeki and T. Shimoda, IEEE Transaction on electron devices, Vol. 49 (2002) 1353.

[2] Y. Hiroshima, R. Ishihara, V. Rana, D. Abe, S. Inoue, T. Shimoda, J.W. Metselaar and C.I.M Beenakker, Dig. Technical Papers AM-LCD 03 (2003) 157.

[3] C. Iriguchi, S. Inoue and T. Shimoda, Dig. Technical Papers AM-LCD 03 (2003) 9.